Strumenti Utente

informatica:ae:aeb1617lezioni

Lezioni AEb 2016-17

Quest'anno il corso AEb fa parte della sperimentazione e-learning UNIPI. I video con le lezioni saranno dunque disponibili sulla mediateca UNIPI. Su questa pagina continuerete a trovare il PDF delle schermate proiettate per la lezione. Il registro ufficiale delle lezioni è quello su Unimap.

| Giorno | Ore | Argomento | Lavagna | Rif. Libro | |

|---|---|---|---|---|---|

| 20 set | 2 | Introduzione al corso. Strutturazione a livelli | I.1 | ||

| 21 set | 2 | Compilazione e interpretazione. Livelli e moduli. Cooperazione ad ambiente locale e globale. Sistema di numerazione binario:rappresentazione di interi (relativi) | I.2, I.3 | ||

| 23 set | 2 | Sistema di numerazione binario: rappresentazione di caratteri e numeri in virgola mobile. Contatori. Operazioni notevoli. | II.1 e II.2 | ||

| 27 set | 2 | Algebra booleana. Reti combinatorie | III.1 | ||

| 28 set | 2 | Reti combinatorie (altri esempi, progettazione modulare). Componente registro e componente memoria. Reti sequenziali: definizione, automi, schema di implementazione, modello Mealy e Moore | III.2 fino a 2.4 escluso | ||

| 29 set | 2 | Reti sequenziali: utilizzo di componenti standard, analisi. Es. reti combinatorie | III completo | ||

| 4 ott | 2 | Esercitazione: reti combinatorie e sequenziali | Primo EsSecondo Es (1.a) | ||

| 5 ott | 2 | Introduzione alle unità firmware: PC e PO. Modello PC-Mealy/PO-Moore. Presentazione del modello di derivazione formale. Esempio con pseudocodice per la divisione fra interi. | IV.1 IV.2 | ||

| 7 ott | 2 | Microlinguaggio. Procedimento formale di derivazione di parte operativa e parte controllo. | IV.2 senza ottimizzazioni | ||

| 7 ott | 2 | Lezione Extra programma: introduzione al Verilog (la lezione non fa parte del programma ufficiale, ma serve da introduzione a chi vuole presentare un progetto al posto della prova scritta) | Dispensa | ||

| 11 ott | 2 | Ottimizzazione di microcodice. Condizioni di Bernstein. Tempo medio di elaborazione e criteri di ottimizzazione. Variabili di condizionamento complesse. Valutazione dell'uso di componenti memoria nelle microistruzioni. | IV fino 3.6 compreso | ||

| 12 ott | 2 | Controllo residuo. Comunicazioni simmetriche a livelli e transizioni di livello | IV 3.7 e IV 4 fino a 4.4 incluso | ||

| 14 ott | 2 | Esercitazione : unità firmware | |||

| 18 ott | 2 | Comunicazioni asincrone: buffer a n posizioni. Comunicazioni asimmetriche: introduzione ai bus. Arbitraggio: arbitri centralizzati e distribuiti. | Cap IV completo. | ||

| 19 ott | 2 | Esercitazione: unità firmware | |||

| 21 ott | 2 | Memoria modulare. Livello macchina assembler: caratteristiche generali, struttura del processore. Compilazione, linking, loading. Processi. Classi di istruzioni e modi di indirizzamento principali. | III.5 (ultima parte), V.1 e V.2 | ||

| 25 ott | 2 | Assembler D-RISC: RISC vs. CISC, insieme di istruzioni base, compilazione di costrutti if, while, for | V fino al V.5.2 incluso | ||

| 28 ott | 1 | Salti ritardati, chiamata di funzione/procedura e modalità di passaggio dei parametri | V.5.4 | ||

| 28 ott | 1 | Esercizi sulla parte firmware | |||

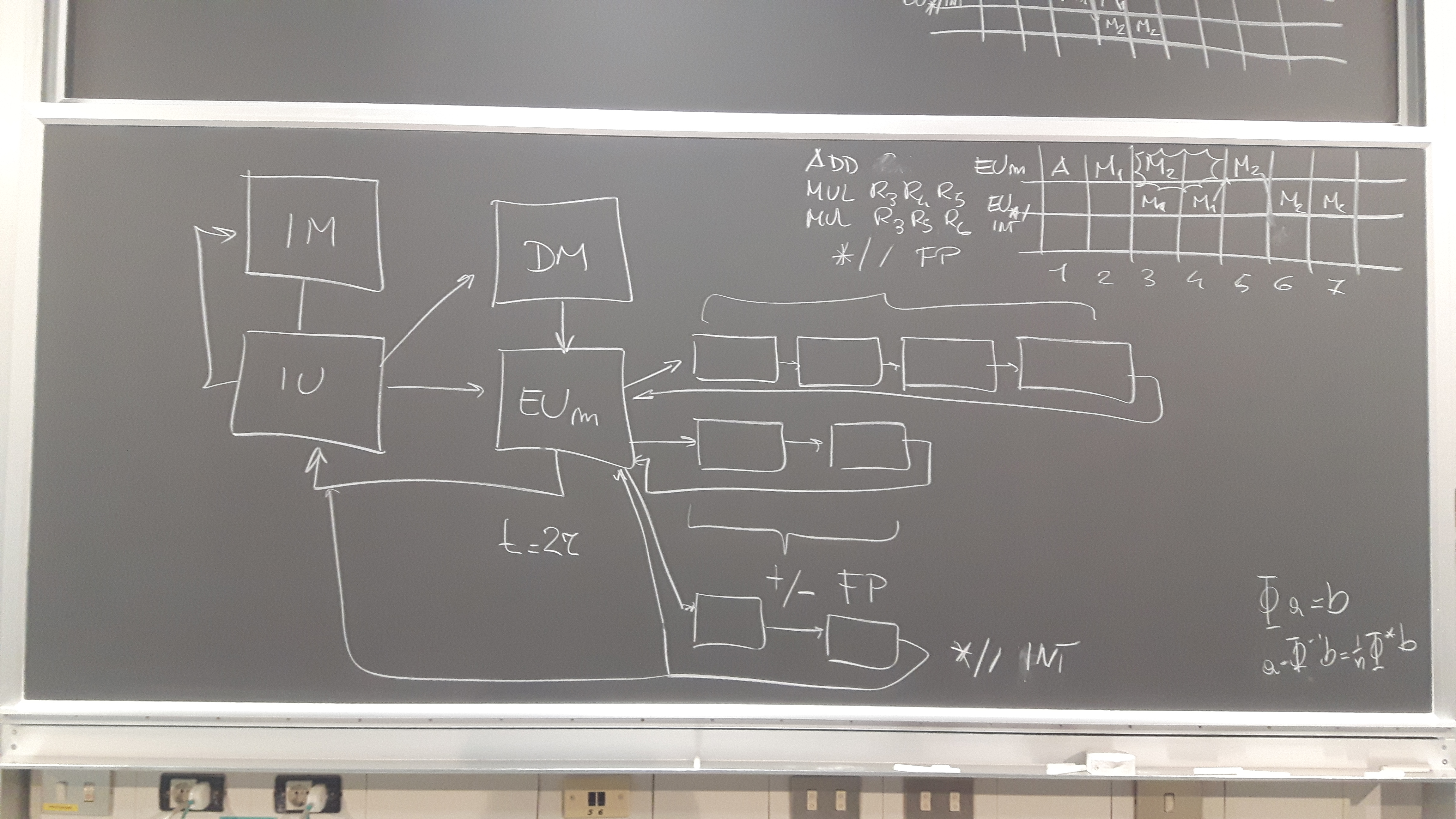

| 8 nov | 2 | Architettura base della CPU e interprete firmware | VII.1 e VII.2 escluso VII.2.4 | ||

| 9 nov | 2 | CPU: struttura PC e PO. Valutazione delle prestazioni | VII.2 e VII.3 | ||

| 11 nov | 2 | Valutazione delle prestazioni: chiarimenti su MIX e Benchmark, peso degli accessi in memoria. Possibilità di miglioramento dell'architettura base: cache, pipeline e superscalare (accenni). Esempio di estensione del set di istruzioni D-RISC e impatto sull'interprete firmware. | Fine cap VII | ||

| 15 nov | 2 | Gerarchie di memoria: paginazione, principi di località e riuso, traduzione degli indirizzi mediante MMU | VIII.1 VIII.2 | ||

| 16 nov | 2 | Cache ad indirizzamento diretto e completamente associativa | VIII.3.1 VIII.3.2 | ||

| 18 nov | 2 | Cache ad indirizzamento associativo su insiemi. Modelli di costo | VIII completo | ||

| 22 nov | 0 | Lezione non tenuta causa missione | |||

| 23 nov | 0 | Lezione non tenuta causa missione | |||

| 25 nov | 2 | Esercitazione: discussione aspetti della prova di verifica + esercizi sulla gerarchia di memoria | |||

| 25 nov | 2 | Lezione di recupero: I/O e trattamento delle interruzioni | Cap. IX | ||

| 29 nov | 2 | Processi: descrittori di processo, scehdulazione a basso livello, istruzione D-RISC START_PROCESS, calcolo di indirizzi fisici (cenno alle capability). | Cap VI fino a 3.2.3 compreso | ||

| 30 nov | 2 | Ulteriori note su traduzione indirizzi e capability. Forme di parallelismo: pipeline (latenza, tempo di servizio e completamento, efficienza e speedup) e farm (introduzione) | X.1, X.9, X.11 | ||

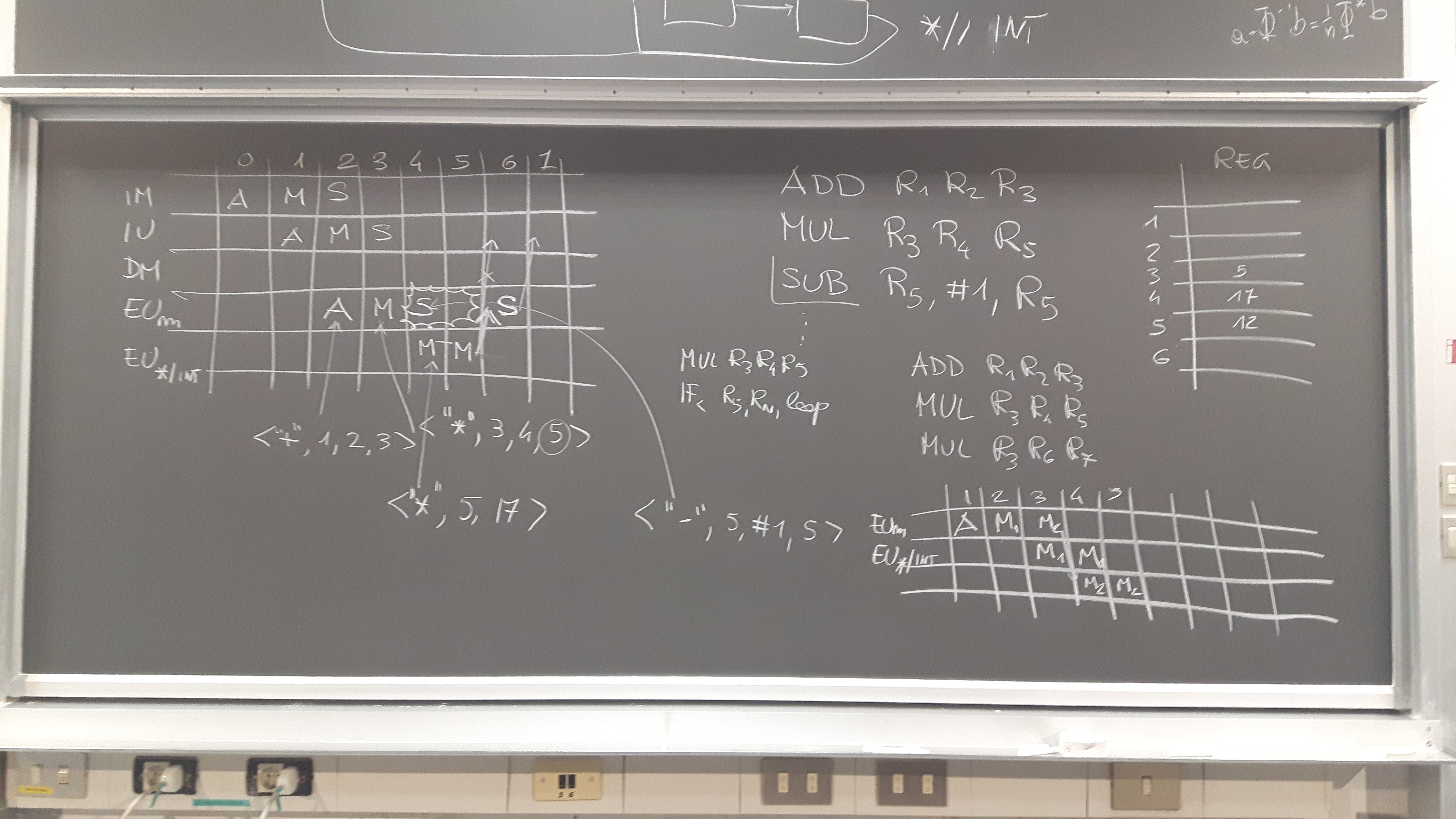

| 2 dic | 2 | Farm (tempo di completamento). Cenni a teoria delle code, fattore di utilizzo delle code e ricerca dei colli di bottiglia (rho > 1). Processore pipeline: struttura e tecniche per la gestione dei registri. | X.11, X.3 (cenni), X.4.1 e X.4.2, XI.1 e XI.2 | ||

| 6 dic | 2 | Dipendenze logiche, salti e degrado delle prestazioni. Valutazione di tempi di servizio, completamento ed efficienza. Impatto della gerarchia di memoria. Esercizi: valutazione delle prestazioni D-RISC Pipeline di semplici codici assembler | XI.3 (senza 3.6 e 3.7) | ||

| 7 dic | 2 | Decodifica Out-of-order nella IU. Unità di esecuzione pipeline per aritmetico logiche lunghe. Dipendenze Eu-EU. Teniche di ottimizzazione del codice per ridurre l'effetto dei salti (inlining, loop unrolling, salto ritardato) | PDF prima ora  PDF seconda ora PDF seconda ora

| XI.8 escluso 8.3, XI.9.1, XI.5.1 | |

| 9 dic | 2 | Tecniche per la minimizzazione dell'effetto delle dipendenze logiche (con esercizi) | |||

| 13 dic | 2 | Architettura superscalare (senza modello dei costi). Multithreading: blocked, interleaving e hyperthreading. | XI.10 (escluso modello dei costi). XI.11.2 (da completare) | ||

| 14 dic | 2 | Supporto fw multithreading. Esercizi | Completamento XI.11.2-5 | ||

| 16 dic | 4 | Esercizi e ripasso “on demand” (Attenzione: nella simulazione del codice del calcolo della f(X) mi sono dimenticato la dipendenza EU-EU fra la prima e la seconda MUL. Guardate le note nel PDF!) | PDF mattina Pomeriggio |

informatica/ae/aeb1617lezioni.txt · Ultima modifica: 16/12/2016 alle 14:09 (7 anni fa) da Marco Danelutto